# 4A, Multi-Chemistry Battery Charger With Photovoltaic Cell MPPT Function CN3795

## **General Descriptions:**

The CN3795 is a PWM switch-mode multi-chemistry battery charger controller that can be powered by photovoltaic cell with maximum power point tracking function using few external components.

The CN3795 is specially designed for charging lithium ion, LiFePO4 or Lithium Titanate batteries with constant current and constant voltage mode. In constant voltage mode, the regulation voltage is set by 2 external resistors. The constant charging current is programmable with a single current sense resistor.

Deeply discharged batteries are automatically trickle charged at 17.5% of the programmed constant charging current until the cell voltage exceeds 66.5% of constant voltage. The charge cycle is terminated once the charging current drops to 16% of full-scale current, and a new charge cycle automatically restarts if the charge current rises above 58.8% of full-scale charge current. CN3795 will automatically enter sleep mode when

input voltage is lower than battery voltage.

Other features include under voltage lockout, battery over voltage protection, status indication, etc.

CN3795 is available in a space-saving 10-pin SSOP package.

## **Applications:**

- Hand-held Equipment

- Emergency Lamp and Camping Lamp

- Battery-Backup Systems

- Portable Industrial and Medical Equipment

- Standalone Chargers for Lithium ion, LiFePO4 or Lithium Titanate Batteries

### **Features:**

- Photovoltaic Cell Maximum Power Point Tracking

- Wide Input Voltage: 6.6V to 30V

- Complete Charge Controller for Singleor Multi-cell Lithium ion, LiFePO4 or Lithium Titanate Batteries

- Charge Current Up to 4A

- PWM Switching Frequency: 310KHz

- Can be used as Voltage Source when Battery is Absent

- Charging Current is programmed with a current sense resistor

- Automatic Conditioning of Deeply Discharged Batteries

- Automatic Recharge

- Charging Status Indication

- Soft Start

- Battery Overvoltage Protection

- Operating Ambient Temperature  $-40^{\circ}$ C to  $+85^{\circ}$ C

- Available in 10-Pin SSOP Package

- Pb-free, Rohs-Compliant, Halogen Free

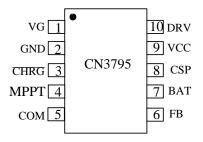

## **Pin Assignment:**

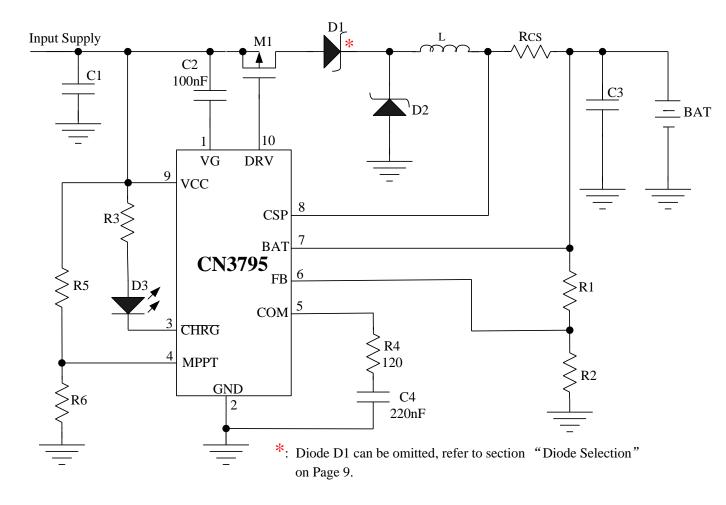

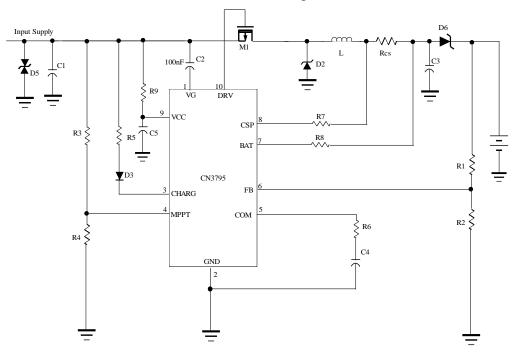

## **Typical Application Circuit:**

## Figure 1 Typical Application Circuit

## **Ordering Information:**

| Part No. | Shipment                 | Operating Ambient Temperature      |  |  |

|----------|--------------------------|------------------------------------|--|--|

| CN3795   | Tape and Reel, 3000/Reel | $-40^{\circ}$ C to $+85^{\circ}$ C |  |  |

## **Pin Description:**

| Pin No.                                                         | Name                                                                    | Descriptions                                                                            |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| 1 VG                                                            |                                                                         | Internal Voltage Regulator. VG internally supplies power to gate driver,                |  |

|                                                                 |                                                                         | connect a 100nF capacitor between VG pin and VCC pin.                                   |  |

| 2                                                               | GND                                                                     | Ground. Negative terminal of input supply.                                              |  |

| 3                                                               |                                                                         | Open-Drain Charge Status Output. When the battery is being charged, this pin            |  |

| 3                                                               | CHRG                                                                    | is pulled low by an internal switch. Otherwise this pin is in high impedance state.     |  |

|                                                                 | Photovoltaic Cell Maximum Power Point Tracking Pin. Connect this        |                                                                                         |  |

| 4                                                               | MPPT                                                                    | the external resistor divider for maximum power point tracking. In maximum              |  |

|                                                                 |                                                                         | power point tracking status, the MPPT pin's voltage is regulated to 1.205V.             |  |

| 5 COM                                                           |                                                                         | <b>Loop Compensation Input.</b> Connect a 220nF capacitor in series with an $120\Omega$ |  |

|                                                                 |                                                                         | resistor from this pin to GND.                                                          |  |

| 6 FB                                                            |                                                                         | Battery Voltage Feedback Input. Generally this Pin is connected to the external         |  |

|                                                                 |                                                                         | feedback resistor divider to sense the battery voltage.                                 |  |

| Negative Input for Charge Current Sensing. This pin and the CSP |                                                                         | Negative Input for Charge Current Sensing. This pin and the CSP pin measure             |  |

| 7                                                               | BAT                                                                     | the voltage drop across the sense resistor $R_{CS}$ to provide the current signals      |  |

|                                                                 |                                                                         | required.                                                                               |  |

|                                                                 |                                                                         | Positive Input for Charge Current Sensing. This pin and the BAT pin measure             |  |

| 8                                                               | CSP                                                                     | the voltage drop across the sense resistor $R_{CS}$ to provide the current signals      |  |

|                                                                 |                                                                         | required.                                                                               |  |

| 9                                                               | <b>External DC Power Supply Input.</b> VCC is also the power supply for |                                                                                         |  |

| 9                                                               | VCC                                                                     | circuit. Bypass this pin with capacitors.                                               |  |

| 10                                                              | DRV                                                                     | Gate Drive Pin. Drive the gate of external P-channel MOSFET.                            |  |

## **Absolute Maximum Ratings**

| Voltage from VCC, CHRG to GND           | 0.3V to 33V  |

|-----------------------------------------|--------------|

| Voltage from VG, DRV to VCC8V to        | VCC+0.3V     |

| Voltage from CSP, BAT to GND            | -0.3V to 25V |

| Voltage from MPPT, COM, FB to GND       | 0.3V to 6.5V |

| Storage Temperature6                    | 5℃ to 150℃   |

| Operating Ambient Temperature           | 40°C to 85°C |

| Lead Temperature(Soldering, 10 seconds) | 260°C        |

Stresses beyond those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

## **Electrical Characteristics:**

| Parameters                                     | Symbol            | Condi                                                                | tions                | Min   | Тур   | Max  | Unit              |

|------------------------------------------------|-------------------|----------------------------------------------------------------------|----------------------|-------|-------|------|-------------------|

| Input Voltage Range                            | VCC               |                                                                      |                      | 6.6   |       | 30   | V                 |

| Under voltage lockout<br>Threshold             | UVLO              |                                                                      |                      | 4     | 5.2   | 6.5  | V                 |

| Operating Current                              | Ivcc              | No switching                                                         |                      | 0.7   | 1.0   | 1.3  | mA                |

| FB Pin Feedback Voltage                        | $V_{FB}$          | Constant voltag                                                      | ge mode              | 1.193 | 1.205 | 1.22 | V                 |

| FB pin Bias Current                            | $I_{FB}$          | V <sub>FB</sub> =1.2V                                                |                      |       | 60    | 300  | nA                |

| Current Sense                                  | V <sub>CS</sub>   | $V_{BAT} > V_{PRE}, V_{CSP} - V_{BAT}$                               |                      | 110   | 120   | 130  | — mV              |

|                                                |                   | V <sub>BAT</sub> <v<sub>PRE, V<sub>CSP</sub>-V<sub>BAT</sub></v<sub> |                      | 10    | 21    | 36   |                   |

| Current into DAT Din                           | I <sub>BAT1</sub> | Termination, V <sub>BAT</sub> =7.4V                                  |                      |       | 10    | 15   |                   |

| Current into BAT Pin                           | I <sub>BAT2</sub> | Sleep mode, $V_{BAT} = 7.4V$                                         |                      |       |       | 15   | uA                |

| Precharge Threshold                            | VPRE              | V <sub>BAT</sub> rises                                               |                      | 64    | 66.5  | 69   | $%V_{REG}$        |

| Precharge Threshold<br>Hysteresis              | H <sub>PRE</sub>  | V <sub>BAT</sub> falls                                               |                      |       | 2.5   |      | %V <sub>REG</sub> |

| Charge Termination<br>Threshold                | I <sub>term</sub> | Charge current decreases                                             |                      |       | 16    |      | %I <sub>CC</sub>  |

| Recharge Threshold                             | V <sub>RE</sub>   | Charge Current Rises                                                 |                      |       | 58.8  |      | %I <sub>CC</sub>  |

| Overvoltage Trip Level                         | Vov               | V <sub>BAT</sub> rises                                               |                      | 1.04  | 1.07  | 1.1  | <b>X</b> 7        |

| Overvoltage Clear Level                        | Vclr              | V <sub>BAT</sub> falls                                               |                      | 1.0   | 1.02  | 1.04 | V <sub>REG</sub>  |

| CHRG Pin                                       |                   |                                                                      |                      |       |       |      |                   |

| CHRG Pin Sink Current                          | ICHRG             | $V_{CHRG}=1V, c$                                                     | harge mode           | 7     | 12    | 18   | mA                |

| CHRG Leakage Current                           | I <sub>LK1</sub>  | V <sub>CHRG</sub> =25V,termination mode                              |                      |       |       | 1    | uA                |

| MPPT Pin                                       |                   |                                                                      |                      |       |       |      |                   |

| MPPT Regulation Voltage                        | V <sub>MPPT</sub> | Maximum pow                                                          | er point track       | 1.18  | 1.205 | 1.23 | V                 |

| MPPT Pin Bias Current                          | I <sub>MPPT</sub> |                                                                      |                      | -100  | 0     | +100 | nA                |

| Oscillator                                     |                   |                                                                      |                      |       |       |      |                   |

| Switching Frequency                            | f <sub>osc</sub>  |                                                                      |                      | 260   | 310   | 360  | kHZ               |

| Maximum Duty Cycle                             | Dmax              |                                                                      |                      |       | 94    |      | %                 |

| Sleep Mode                                     |                   |                                                                      |                      |       |       |      |                   |

| Sleep Mode Threshold (measure VCC $-V_{BAT}$ ) | V <sub>SLP</sub>  | VCC falling                                                          | V <sub>BAT</sub> =8V | 0.0   | 0.05  | 0.1  | V                 |

| Sleep mode Release                             | N7                | NCC rising                                                           | V - 9V               | 0.2   | 0.22  | 0.46 | V                 |

| Threshold                                      | V <sub>SLPR</sub> | VCC rising,                                                          | V <sub>BAT</sub> =8V | 0.2   | 0.32  | 0.46 | V                 |

| (measure VCC $-V_{BAT}$ )                      |                   | 1                                                                    |                      | 1     |       |      |                   |

| DRV Pin                                        | VII               | I — 10: 4                                                            |                      |       | 60    |      | m V               |

| $V_{DRV}$ High (VCC – $V_{DRV}$ )              | VH                | $I_{DRV} = -10 \text{mA}$                                            |                      |       | 60    |      | mV                |

| V <sub>DRV</sub> Low (VCC-V <sub>DRV</sub> )   | VL t              | $I_{DRV} = 0 \text{mA}$                                              |                      | 30    | 6.3   | 65   | V<br>no           |

| Rise Time                                      | t <sub>r</sub>    | Cload = 2nF, 10%  to  90%                                            |                      |       | 40    | 65   | ns                |

| Fall Time                                      | $t_{\rm f}$       | Cload=2nF, 90% to 10%                                                |                      | 30    | 40    | 65   | ns                |

(VCC=15V,  $T_A$ =-40°C to 85°C, unless otherwise noted)

Note:  $V_{REG}$  is the regulated voltage in constant voltage mode;  $I_{CC}$  is the charge current in constant current mode.

## **Detailed Description:**

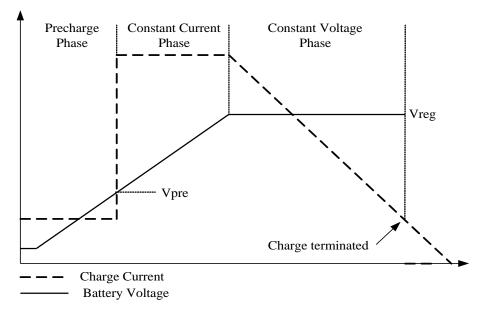

The CN3795 is a constant current, constant voltage battery charger controller that can be powered by the photovoltaic cell with maximum power point tracking function. The CN3795 adopts PWM step-down (buck) switching architecture, and can be used to charge single- or multi-cell Lithium ion battery, LiFePO4 or Lithium Titanate batteries. The charge current is set by an external sense resistor ( $R_{CS}$ ) across the CSP and BAT pins. The final battery regulation voltage in constant voltage mode can be set by 2 feedback resistors at FB pin. A charge cycle begins when the voltage at the VCC pin rises above the UVLO level and is greater than the battery voltage by  $V_{SLPR}$ . At the beginning of the charge cycle, if the battery voltage is less than 66.5% of regulation voltage ( $V_{REG}$ ), the charger goes into trickle charge mode. The trickle charge current is internally set to 17.5% (Typical) of the full-scale current. When the battery voltage exceeds 66.5% of regulation voltage, the charger goes into the full-scale constant current charge mode. In constant current mode, the charge current is set by the external sense resistor  $R_{CS}$  and an internal 120mV reference, the charge goes into constant voltage mode, and the charge current will start to decrease. When the charge current drops to 16% of the full-scale current, the charge current will start to decrease. When the charge current drops to 16% of the full-scale current, the charge pin to indicate the termination status.

To restart the charge cycle, just remove and reapply the input voltage. Also, a new charge cycle will begin if the charge current rises above the recharge threshold of 58.8% of the full-scale charge current.

The CN3795 adopts the constant voltage method to track the photovoltaic cell's maximum power point. The MPPT pin's voltage is regulated to 1.205V to track the maximum power point of the photovoltaic cell. When the input voltage is not present, the charger automatically goes into sleep mode, all the internal circuits are shutdown.

An overvoltage comparator guards against voltage transient overshoots (>7% of regulation voltage). In this case, the external P-channel MOSFET are turned off until the overvoltage condition is cleared. This feature is useful for battery load dump or sudden removal of battery.

The charging profile is shown in Figure 2.

## Figure 2 The Charging Profile

## **Application Information**

### Under voltage Lockout (UVLO)

An under voltage lockout circuit monitors the input voltage and keeps the charger off if VCC falls below 6.5V(Maximum).

### **Trickle Charge Mode**

At the beginning of a charge cycle, if the battery voltage is below 66.5% of the regulation voltage, the charge goes into trickle charge mode with the charge current reduced to 17.5% of the full-scale current.

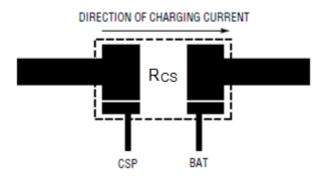

### **Charge Current Setting**

The full-scale charge current, namely the charge current in constant current mode, is decided by the following formula:

ICH =

$$\frac{120\text{mV}}{\text{Rcs}}$$

Where:

$I_{\rm CH}$  is the full scale charge current

$R_{CS}$  is the resistor between the CSP pin and BAT pin

### Set the Regulation Voltage

As shown in Figure 1, battery voltage is feedback to FB pin via the resistor divider composed of R1 and R2. CN3795 decided the charging status based on FB's voltage. When FB's voltage approaches 1.205V, the charger goes into constant voltage mode. In constant voltage mode, the charge current decrease gradually, and the battery voltage remains unchanged.

In light of FB pin's bias current, the regulation voltage in constant voltage mode is determined by the following equation:

$$V_{REG} = 1.205 \times (1 + R1 / R2) + I_B \times R1$$

Where, I<sub>B</sub> is FB pin's bias current, which is 60nA typical.

From the above equation, we can see that an error is introduced due to the existence of bias current  $I_B$ , the error is  $I_B \times R1$ . If  $R1 = 500 K\Omega$ , then the error is about 30mV. So the error should be taken into account while designing the resistor divider.

The maximum regulation voltage that can be set is 25V.

### The Maximum Power Point Tracking

CN3795 adopts the constant voltage method to track the photovoltaic cell's maximum power point. From I-V curve of photovoltaic cell, under a given temperature, the photovoltaic cell's voltages at the maximum power point are nearly constant regardless of the different irradiances. So the maximum power point can be tracked if the photovoltaic cell's output voltage is regulated to a constant voltage.

CN3795's MPPT pin's voltage is regulated to 1.205V to track the maximum power point working with the off-chip resistor divider(R5 and R6 in Figure 1).

The maximum power point voltage is decided by the following equation:

$V_{MPPT} = 1.205 \times (1 + R5 / R6)$

### **Charge Termination**

In constant voltage mode, the charge current decreases gradually. When the charge current decreases to 16% of the full-scale current, the charging is terminated. In charge termination mode, CHRG pin outputs high impedance to indicate the charge termination mode, and CN3795 will continue to charge the battery in constant voltage mode to ensure that the battery is fully charged.

In photovoltaic cell's maximum power point tracking mode, the charging will not be terminated until the battery voltage is higher than 95.8% of the regulation voltage set by the feedback resistors at FB pin, even though the

charge current is lower than 16% of the full-scale current.

### **Automatic Recharge**

After the charge cycle is completed and both the battery and the input power supply (wall adapter) are still present, a new charge cycle will begin if the charge current rises above 58.8% of the full-scale charge current due to self-discharge or external loading.

#### **Status Indication**

The CN3795 has one open-drain status output:  $\overline{CHRG}$ .  $\overline{CHRG}$  pin is pulled low when the charger is in charging status, otherwise  $\overline{CHRG}$  becomes high impedance.

The  $\overline{CHRG}$  pin should be tied to ground if not used.

The table 1 lists the indicator status and its corresponding charging status. It is supposed that red LED is connected to  $\overline{CHRG}$  pin.

| CHRG pin                        | State Description                              |  |  |

|---------------------------------|------------------------------------------------|--|--|

| Low(the red LED on)             | Charging                                       |  |  |

|                                 | There are 3 possible reasons:                  |  |  |

|                                 | • Charge termination, or                       |  |  |

| High Impedance(the red LED off) | • The voltage at the VCC pin is below the UVLO |  |  |

|                                 | level, or                                      |  |  |

|                                 | • The voltage at the VCC pin below $V_{BAT}$   |  |  |

## Table 1 Indication Status

#### **Gate Drive**

The CN3795's gate driver can provide high transient currents to drive the external pass transistor. The rise and fall times are typically 40ns when driving a 2000pF load, which is typical for a P-channel MOSFET with Rds(on) in the range of  $30m \Omega$ .

A voltage clamp is added to limit the gate drive to 8V max. below VCC. For example, if VCC is 20V, then the DRV pin output will be pulled down to 12V min. This allows low voltage P-channel MOSFETs with superior Rds(on) to be used as the pass transistor thus increasing efficiency.

#### **Loop Compensation**

In order to make sure that the current loop and the voltage loop are stable, a series-connected 220nF ceramic capacitor and  $120 \Omega$  resistor from the COM pin to GND are necessary.

### CN3795 used as Voltage Source

The CN3795 can be used as a voltage source when battery is absent. The voltage of the source is the regulation voltage set by 2 external feedback resistors, namely R1 and R2 in Figure 1. The maximum output current of the voltage source is the full-scale current set by current sense resistor  $R_{CS}$ .

#### **Input Capacitors**

Since the input capacitor(C1 in Figure 1) is assumed to absorb all input switching ripple current in the converter, it must have an adequate ripple current rating. Worst-case RMS ripple current is approximately one-half of output charge current.

In order to depress the high-frequency oscillation during P-channel MOSFET's turning on and off, it is best that the input capacitor consists of the following 3 capacitors in parallel:

- Electrolytic capacitor for low-frequency filtering

- A ceramic capacitor from 1uF to 10uF

- A high-frequency capacitor from 47nF to 1uF

### **Output Capacitors**

The selection of output capacitor (C3 in Figure 1) is primarily determined by the ESR required to minimize ripple voltage and load step transients. it is best that the output capacitor consists of the following 2 capacitors in parallel:

- A 10uF electrolytic capacitor for low-frequency filtering

- A ceramic capacitor from 1uF to 10uF

If only ceramic capacitor can be used, cares must be taken that some ceramic capacitors exhibit large voltage coefficient, which may lead to high voltage at BAT pin when battery is not present. In this case, the capacitor value should be increased properly so that no damage will be done.

#### **Inductor Selection**

During P-channel MOSFET's on time, the inductor current increases, and decreases during P-channel MOSFET's off time, the inductor's ripple current increases with lower inductance and higher input voltage. Higher inductor ripple current results in higher charge current ripple and greater core losses. So the inductor's ripple current should be limited within a reasonable range.

The inductor's ripple current is given by the following formula:

$$\Box I_{L} = \frac{1}{(f)(L)} V_{BAT} (1 - \frac{V_{BAT}}{VCC})$$

Where,

f is the switching frequency 310KHz

L is the inductor value

$V_{\text{BAT}}$  is the battery voltage

VCC is the input voltage

A reasonable starting point for setting inductor ripple current is  $\triangle I_L = 0.3 \times I_{CH}$ ,  $I_{CH}$  is the charge current. Remember that the maximum  $\triangle I_L$  occurs at the maximum input voltage and the lowest inductor value. So lower charge current generally calls for larger inductor value.

In the meantime, inductor value should meet the requirement of the following equation:

$L > 5 X (VCC-VBAT) \qquad (uH)$

### **MOSFET Selection**

The CN3795 uses a P-channel power MOSFET switch. The MOSFET must be selected to meet the efficiency or power dissipation requirements of the charging circuit as well as the maximum temperature of the MOSFET. The peak-to-peak gate drive voltage is set internally, this voltage is typically 6.3V. Consequently, logic-level threshold MOSFETs must be used. Pay close attention to the BV<sub>DSS</sub> specification for the MOSFET as well; many of the logic-level MOSFETs are limited to 30V or less.

Selection criteria for the power MOSFET includes the "on" resistance Rds(on), total gate charge Qg, reverse transfer capacitance C<sub>RSS</sub>, input voltage and maximum current.

The MOSFET power dissipation at maximum output current is approximated by the equation:

$$Pd = \frac{VBAT}{VCC} \times Rds(on) \times ICH^2 \times (1+0.005dT)$$

Where:

Pd is the power dissipation of the power MOSFET VBAT is the maximum battery voltage VCC is the minimum input voltage Rds(on) is the power MOSFET's on resistance at room temperature ICH is the charge current

dT is the temperature difference between actual ambient temperature and room temperature(25 °C) In addition to the I<sup>2</sup>Rds(on) loss, the power MOSFET still has transition loss, which are highest at the highest input voltage. Generally speaking, for VIN<20V, the I<sup>2</sup>Rds(on) loss may be dominant, so the MOSFET with lower Rds(on) should be selected for better efficiency; for VIN>20V, the transition loss may be dominant, so the MOSFET with lower C<sub>RSS</sub> can provide better efficiency. C<sub>RSS</sub> is usually specified in the MOSFET characteristics; if not, then C<sub>RSS</sub> can be calculated using C<sub>RSS</sub> = Q<sub>GD</sub>/ $\Delta$ V<sub>DS</sub>.

The MOSFETs such as CN2305, 4459, 4435, 9435, 3407A can be used. The part numbers listed above are for reference only, the users can select the right MOSFET based on their requirements.

#### **Diode Selection**

The diodes D1 and D2 in Figure 1 are schottky diode, the current rating of the diodes should be at least the charge current limit, the voltage rating of the diode should exceed the maximum expected input voltage. The diode that is much larger than that is sufficient can result in larger transition losses due to their larger junction capacitance.

Diode D1 in Figure 1 is used as block diode to prevent battery current from flowing back to VCC when input supply is absent. Without D1, CN3795 consumes about 51uA current from battery( $V_{BAT}=8V$ ), so diode D1 can be removed if the 51uA battery current is not a consideration.

#### **Battery Current In Sleep Mode**

In the typical application circuit shown in Figure 1, when input voltage is powered off or lower than battery voltage, CN3795 will enter sleep mode. In sleep mode, the battery current includes:

- (1) The current into BAT pin and CSP pin, which is about  $10uA(V_{BAT}=8V)$ .

- (2) The current from battery to VCC pin via diode D1, which is determined by D1's leakage current. If diode D1 is not used, then the current flowing to VCC pin via inductor and body diode of P-channel MOSFET is about 42uA(V<sub>BAT</sub>=8V).

- (3) The current from battery to GND via diode D2, which is also determined by D2's leakage current.

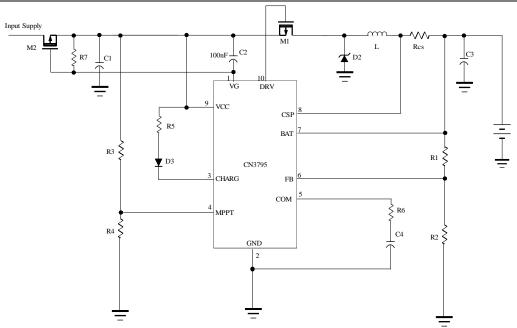

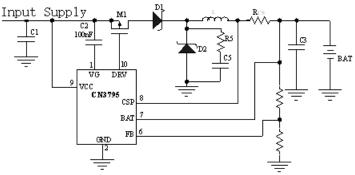

# Using PMOS transistor to realize reverse connection protection of input power supply and prevent battery current backflow

In a typical application, diode D1 in figure 1 is used to prevent battery current backflow. However, due to the conduction voltage drop of the diode, when the current flowing through is relatively large, the power consumption of the diode is relatively large. In order to solve this problem, in the circuit in Fig. 3, the PMOS transistor M2 is used instead of the diode D1, which can not only prevent the battery current from flowing back, but also realize the reverse connection protection function of the input power supply.

In general, the technical requirements of PMOS transistor M2 are: the Vds must be greater than the maximum input power supply voltage, the Vgs must be greater than the battery voltage, and the on resistance and maximum drain current Id meet the requirements of charging current. Resistance R7 is generally 22K ohm.

## Figure 3 using PMOS to realize power reverse connection protection and

## prevent battery current backflow

### High voltage input and output considerations

When the input power supply voltage is greater than 20V or the constant voltage charging voltage is set to exceed 20V, due to the influence of the parasitic inductance of the wire, the input and output filter capacitance and the parasitic capacitance caused by the layout and wiring of the PCB board, an overshoot voltage is generated at the moment of power on or power off and the moment of battery on and off, which may damage the CN3795 in some cases. At this time, refer to the circuit of Fig. 4.

Figure 4 high voltage optimization circuit

#### Of which:

D5, transient suppression tube, 28V TVs tube can be selected;

D6, Schottky diode, the same model as D2;

R9, resistance, optional 5.1 ohm, 0805 package resistance;

R7, resistance, optional 100 ohm, 0603 package resistance;

R8, resistance, selectable 100 ohm, 0603 package resistance;

C5, capacitor, 10uF, 0805 encapsulated ceramic capacitor can be selected.

#### About the suppression of high frequency oscillation

In the case of high input voltage or large charging current, if the PCB layout and wiring are unreasonable, or the parasitic inductance of diode and p-channel FET is relatively large, high-frequency oscillation above 10MHz will be generated at the moment when p-channel FET is turned on or off. High frequency oscillation waveform can be observed on the positive pole of input power supply and the negative pole of diode D2 with oscilloscope. In order to suppress high-frequency radiation, in addition to improving PCB layout and wiring, high-frequency suppression circuits can also be added, such as R5 and C5 in Fig. 5.

Figure 5 high frequency oscillation suppression

#### **PCB Layout Considerations**

When laying out the printed circuit board, the following considerations should be taken to ensure proper operation of the IC.

- (1) To minimize radiation, the 2 diodes, pass transistor, inductor and the input bypass capacitor traces should be kept as short as possible. The positive side of the input capacitor should be close to the source of the P-channel MOSFET; it provides the AC current to the pass transistor. The connection between the diode and the pass transistor should also be kept as short as possible.

- (2) The compensation capacitor connected at the COM pin, the resistor divider at MPPT pin and feedback resistor at FB pin should return to the ground pin of the IC. This will prevent ground noise from disrupting the loop stability.

- (3) Place R1,R2,R4,R5,R6 and C4 as close to the CN3795 as possible.

- (4) Output capacitor ground and catch diode (D2 in Figure 1) ground connections need to feed into same copper that connects to the input capacitor ground before tying back into system ground.

- (5) Analog ground and power ground(or switching ground) should return to system ground separately.

- (6) The ground pins also works as a heat sink, therefore use a generous amount of copper around the ground pins. This is especially important for high VCC and/or high gate capacitance applications.

- (7) Place the charge current sense resistor R<sub>CS</sub> right next to the inductor output but oriented such that the IC's CSP and BAT traces going to R<sub>CS</sub> are not long. The 2 traces need to be routed together as a single pair on the same layer at any given time with smallest trace spacing possible.

(8) The CSP and BAT pins should be connected directly to the 2 terminals of current sense resistor (Kelvin sensing) for best charge current accuracy. See Figure 6 as an example.

Figure 6 Kelvin Sensing of Charge Current

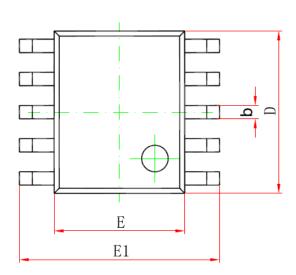

## **Package Information**

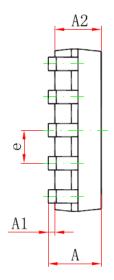

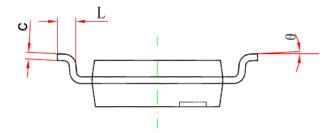

| Symbol | Dimensions In Millimeters |                      | Dimensions In Inches |        |  |

|--------|---------------------------|----------------------|----------------------|--------|--|

|        | Min                       | Max                  | Min                  | Max    |  |

| А      | 1.350                     | 1. 750               | 0.053                | 0.069  |  |

| A1     | 0.100                     | 0. 250               | 0.004                | 0.010  |  |

| A2     | 1.350                     | 1. <mark>5</mark> 50 | 0.053                | 0.061  |  |

| b      | 0. 300                    | 0.450                | 0.012                | 0. 018 |  |

| с      | 0.170                     | 0. 250               | 0.007                | 0.010  |  |

| D      | 4. 700                    | 5. 100               | 0. 185               | 0. 201 |  |

| E      | 3.800                     | 4. 000               | 0. 150               | 0. 157 |  |

| E1     | 5.800                     | 6.200                | 0. 228               | 0. 244 |  |

| е      | 1.000 (BSC)               |                      | 0. 039 (BSC)         |        |  |

| L      | 0. 400                    | 1. 270               | 0.016                | 0. 050 |  |

| θ      | 0°                        | 8°                   | 1 °                  | 8 °    |  |

Consonance does not assume any responsibility for use of any circuitry described. Consonance reserves the right to change the circuitry and specifications without notice at any time.